Учебное пособие 1492

.pdf

10.В появившемся окне, в строке Print Step записать 1u, а в строке Final Time 10u.

11.Нажать OK.

12.Нажать Close.

13.Запустить схему на анализ, щёлкнув мышкой по кнопке 5 (рис. 5.1).

Значения вводимых параметров генераторов для D- триггера, представленного на рис. 5.4. даны в таблице 5.1

Таблице 5.1

Тип ге- |

|

ON- |

OFFTI |

START |

OPPVA |

|

нерато- |

DELAY |

|||||

TIME |

ME |

VAL |

L |

|||

ра |

|

|||||

|

|

|

|

|

||

DSTM1 |

1us |

1us |

1us |

0 |

1 |

|

DSTM2 |

1.5us |

0.1us |

2.9us |

0 |

1 |

|

|

|

|

|

|

|

|

DSTM3 |

0.1us |

10us |

1us |

0 |

1 |

|

|

|

|

|

|

|

5.2. ИССЛЕДОВАНИЕ D- И RS-ТРИГГЕРОВ

При выполнении схемотехнического моделирования цифрового устройства необходимо разработать задание на моделирование, ввести заданные параметры генераторов сигналов, снять временные диаграммы работы цифрового устройства, построить таблицу истинности моделируемого устройства.

5.2.1. Схемотехническое моделирование D - триггера, входящего в состав микросхемы 7474 (отечественный ана-

лог К155ТМ2)

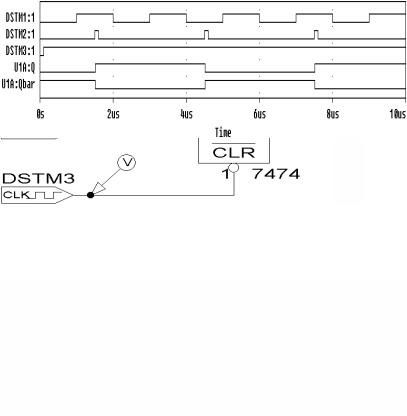

Схема измерения для проведения данной работы приведена на рис. 5.4.

Временные диаграммы работы D - триггера приведены на рис. 5.5. Таблица истинности приведена в табл. 5.2.

Рис. 5.4. Схема измерения D – триггера, входящего в состав микросхемы 7474

Рис. 5.5. Временные диаграммы работы D - триггера

Таблица 5.2

Таблица истинности D – триггера

DSTM1 |

DSTM2 |

DSTM3 |

U1A |

D |

CLK |

CLR |

Q |

|

|

|

|

Х |

Х |

0 |

0 |

Х |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

80 |

81 |

5.2.2. Схемотехническое моделирование инверсного RS – триггера, построенного на логических элементах И – НЕ, входящих в состав микросхемы 7400 (отечественный аналог К155ЛА3).

Схема измерения и временные диаграммы работы инверсного RS – триггера построенного на логических элементах И – НЕ, приведены на рис. 5.6 и 5.7 соответственно.

Рис. 5.6. Схема измерения инверсного RS – триггера

Рис. 5.7. Временные диаграммы сигналов инверсного RS

– триггера

Таблица 5.3 Форма таблицы истинности инверсного RS – триггера построенного на логических элементах И – НЕ

DSTM1 |

DSTM2 |

|

|

U1A |

U2A |

||

R |

|

|

S |

|

|

Q |

Q |

|

|

|

|||||

5.2.3. Схемотехническое моделирование RS - триггера построенного на логических элементах ИЛИ - НЕ, входящих в состав микросхемы 7402 (отечественный аналог К155ЛЕ1).

Схема измерения и временные диаграммы работы RS – триггера, построенного на логических элементах ИЛИ – НЕ, приведены на рис. 5.8 и 5.9 соответственно.

Рис.5.8. Схема измерения RS - триггера, построенного на основе логических элементов ИЛИ - НЕ

82 |

83 |

Рис.5.9. Временные диаграммы сигналов RS – триггера, построенного на основе логических элементов ИЛИ - НЕ

Таблица 5.4 Форма таблицы истинности RS – триггера, построенного

на логических элементах И – НЕ.

DSTM1 |

DSTM2 |

U1A |

U2A |

R |

S |

Q |

Q |

5.2.4. Схемотехническое моделирование стартстопного устройства, построенного на трех логических элементах И - НЕ, входящих в состав микросхемы 7400 (отечествен-

ный аналог К155ЛА3).

Схема измерения и временные диаграммы стартстопного устройства, построенного на трех логических элементах И - НЕ, приведены на рис. 5.10 и 5.11 соответственно.

Таблица 5.5 Форма таблицы истинности стартстопного устройства, построенного на трех логических элементах И – НЕ.

DSTM |

DSTM |

DSTM |

|

U1A |

U2A |

U3A |

1 |

2 |

3 |

|

Q |

Q |

Y |

ТИ |

Старт |

стоп |

|

|

|

|

|

|

|

84 |

|

|

|

Рис. 5.10 Схема измерения стартстопного устройства, построенного на трех логических элементах И – НЕ

Рис. 5.11. Временные диаграммы сигналов стартстопного устройства, построенного на трех логических элементах И – НЕ

5.3. ВВОДИМЫЕ ПАРАМЕТРЫ ГЕНЕРАТОРОВ

85

Таблица 5.6 Вводимые параметры генераторов цифровых сигналов

для лабораторных заданий

№ |

№ |

Источ- |

П А Р А М Е Т Р Ы |

|

|

||

|

|

ник |

|

|

|

|

|

Зад– |

Вар |

|

DELAY |

ONTIME |

OFFTIME |

START- |

OPPVAL |

я |

. |

|

|

|

|

VAL |

|

|

|

|

|

|

|

||

|

|

DSTM1 |

1Us |

3Us |

2Us |

0 |

1 |

|

1 |

DSTM2 |

1Us |

1Us |

1Us |

0 |

1 |

|

|

DSTM3 |

1Us |

5Us |

5Us |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

HI |

– – – |

– – – |

– – – |

– – – – |

– – – |

|

|

DSTM1 |

0.5Us |

2Us |

4Us |

0 |

1 |

1 |

2 |

DSTM2 |

2Us |

1Us |

2Us |

0 |

1 |

|

|

DSTM3 |

0.5Us |

3Us |

4Us |

0 |

1 |

|

|

O |

– – – |

– – – |

– – – |

– – – – |

– – – |

|

|

|

|

|

|

|

– |

|

|

DSTM1 |

1Us |

1Us |

1Us |

0 |

1 |

|

3 |

DSTM2 |

1.5Us |

2Us |

3Us |

0 |

1 |

|

|

DSTM3 |

2Us |

25Us |

1Us |

0 |

1 |

|

|

HI |

– – – |

– – – |

– – – |

– – – |

– – – |

|

1 |

DSTM1 |

1Us |

4Us |

1Us |

0 |

1 |

|

|

DSTM2 |

3Us |

1Us |

5Us |

0 |

1 |

2 |

2 |

DSTM1 |

2Us |

5Us |

3Us |

0 |

1 |

|

|

DSTM2 |

2.5Us |

2Us |

3Us |

0 |

1 |

|

3 |

DSTM1 |

1Us |

2Us |

2Us |

0 |

1 |

|

|

DSTM2 |

2Us |

2Us |

1Us |

0 |

1 |

|

1 |

DSTM1 |

2Us |

2Us |

2Us |

0 |

1 |

|

|

DSTM2 |

1Us |

1Us |

1Us |

0 |

1 |

3 |

2 |

DSTM1 |

0.5Us |

1Us |

2.6Us |

0 |

1 |

|

|

DSTM2 |

2.2Us |

1Us |

0.5Us |

0 |

1 |

|

3 |

DSTM1 |

1.5Us |

2.5Us |

3Us |

0 |

1 |

|

|

DSTM2 |

3Us |

2.5Us |

1.5Us |

0 |

1 |

|

|

DSTM1 |

2Us |

1Us |

1Us |

0 |

1 |

|

|

|

|

|

Продолжение табл. 5.6 |

||

|

1 |

DSTM2 |

2Us |

4Us |

10Us |

1 |

0 |

|

|

DSTM3 |

10Us |

5Us |

10Us |

0 |

1 |

4 |

|

DSTM1 |

1Us |

2.5Us |

1.6Us |

0 |

1 |

2 |

DSTM2 |

2Us |

5Us |

2.5Us |

1 |

0 |

|

|

|

DSTM3 |

5Us |

3.3Us |

1Us |

0 |

1 |

|

|

DSTM1 |

0.5Us |

2Us |

1Us |

0 |

1 |

|

3 |

DSTM2 |

2.2Us |

1.5Us |

2.5Us |

0 |

1 |

|

|

DSTM3 |

3Us |

10Us |

2.6Us |

0 |

1 |

5.4.СОДЕРЖАНИЕ ОТЧЕТА

1.Схемы измерения триггеров.

2.Значения параметров цифровых сигналов.

3.Значения параметров анализа переходных характеристик

(Transient).

4.Временные диаграммы работы триггеров и стартстопного устройства.

5.Таблицы истинности.

6.Обсуждение результатов, выводы по работе.

86 |

87 |

7. КОМПЬЮТЕРНЫЙ АНАЛИЗ JK-ТРИГГЕРОВ

Цель исследования. Приобрести навыки схемотехнического моделирования JK-триггеров при помощи ПЭВМ в среде программной системы DesignCenter.

Содержание исследования. В исследовании выполняет-

ся схемотехническое моделирование JK-триггеров SN7470 на ПЭВМ. Схемотехническое моделирование включает три основных этапа: составление задания на моделирование, ввод параметров генераторов, снятие временных диаграмм и построение таблиц истинности. Кроме того, по указанному алгоритму производится моделирование ряда других комбинационных интегральных микросхем согласно индивидуальному заданию.

Подготовительный этап. JK-триггер наиболее широко используемый универсальный триггер, обладающий характеристиками всех других типов.

Проработать разделы "Назначение и классификация триггерных устройств" [1, с.553-556], "JK-триггеры" [1, с. 565566; 6, с. 149-162; 8, с. 354-355; 9, с. 277-281; 11, с. 221-222]

6.1. ОБЩИЕ УКАЗАНИЯ ПО ПРОВЕДЕНИЮ АНАЛИЗА

1.Активировать программную систему Design Center.

2.Загрузить графический редактор Shematics.

3.При необходимости создания новой схемы щелкнуть мышкой на кнопку 2, показанную на рис.6.1.

4.Достать из библиотеки необходимые элементы. Для этого: а) щелкнуть мышкой на кнопку 3 (рис.6.1);

б) в появившемся окне (рис. 6.2),в строке Part Name за-

писать условное обозначение элемента ( 7493А ); в) нажать кнопку Place;

г) чтобы из библиотеки достать генератор импульсов, в строке Part Name нужно записать DigCloсk;

д) нажать кнопку Place&Close.

Рис. 6.1. Панель инструментов Shematics

5.Расставить элементы в нужном порядке.

6.Провести соединительные линии. Для этого предварительно необходимо щелкнуть мышкой по кнопке 1 (рис.6.1).

Рис. 6.2. Окно содержания элементов в библиотеках

7. Задать параметры генераторов. Для этого:

а) дважды щелкнуть мышкой по его изображению;

88 |

89 |

б) в появившемся окне (рис.6.3) выбрать необходимый параметр;

в) в строке Value записать его значение и нажать Enter ; г) после ввода всех необходимых параметров щелкнуть

по кнопке OK.

В данном задании параметры для генератора DSTM 1 :DELAY = 2uS , ONTIME = 0.5uS , OFFTIME = 0.5uS , STARTVAL = 0 , OPPVAL = 1 . DELAY = 1uS , ONTIME = 1uS , OFFTIME = 100uS , STARTVAL = 0 , OPPVAL = 1.

Рис. 6.3. Окно параметров генератора.

8.Расставить значки ( вольтметры ) с помощью клавиш Ctrl+M. Расставлять, начиная с младшего разряда на выходе.

( вольтметры ) с помощью клавиш Ctrl+M. Расставлять, начиная с младшего разряда на выходе.

9.Установить параметры анализа, щёлкнув по кнопке 4 (рис.6.1).

10. Затем щелкнуть мышкой по кнопке Transient.

11.В появившемся окне в строке Print Step записать 1u, а

встроке Final Time 20u

12.Нажать OK.

13.Нажать Close.

14.Запустить схему на анализ щёлкнув мышкой по кнопке 5 (рис.6.1).

15.Составить таблицу истинности, нажав кнопку Cursor

ипередвигая куроср по временным диограммам.

Для проведения данной работы представлено несколько видов микросхем ,а так же их функциональный состав, а именно JK-триггеры: 7470, 7472 (отечественный аналог К155ТВ1), 74107 ( К155ТВ6 ), 74109 (155ТВ15 ), 74110, 74111.

6.2ИССЛЕДОВАНИЕ JK-ТРИГГЕРОВ

6.2.1.Схемотехническое моделирование синхронного триггера на микросхеме 7470

Микросхема 7470 представляет собой синхронный триггер, имеющий по три входа J и K, один из которых инверсный,

атак же сброс - CLR , и предустановку - PRE . Для проведения схемотехнического моделирования необходимо:

1)Составить задание на моделирование, используя схему измерения , выполнив пункты 1-13 алгоритма .

2)Снять временные диаграммы работы JK=триггера, выполнив пункт 14 алгоритма.

3)Составить таблицу истинности JK-триггера, выполнив пункт 15 алгоритма.

Схема измерения триггера приведена на рис. 6.4, на рис.

6.5представлены временные диаграммы, форма таблицы истинности - в табл. 6.1.

Таблица 6.1 Таблица истинности работы триггера 7470

|

|

|

|

|

|

_ |

S |

R |

C |

J |

K |

Q |

Q |

0 |

0 |

X |

X |

X |

1 |

1 |

1 |

0 |

X |

X |

X |

0 |

1 |

0 |

1 |

X |

X |

X |

1 |

0 |

1 |

1 |

↑ |

0 |

1 |

0 |

1 |

1 |

1 |

↓ |

1 |

0 |

1 |

0 |

90 |

91 |

Рис. 6.4. Схема измерения триггера 7470

Рис. 6.5. Временные диаграммы триггера 7470

6.2.2. Индивидуальные задания для схемотехнического моделирования

Распределение индивидуальных заданий по группам следующее:

Группа ..1 – JK-триггеры 7472,74107.

Группа ..2 – JK-триггеры 74109, 74110.

Группа ..3 – JK-триггеры 74111, 7472 ( построенный на логических элементах).

В пределах группы первая подгруппа использует первый из указанных триггеров, вторая подгруппа – второй.

JK-триггер 74109, построенный на логических элементах, используется как резервный.

Параметры генераторов задать из табл. 6.6.

Для проведения схемотехнического моделирования необходимо:

1)Составить задание на моделирование, используя схему измерения, выполнив пункты 1-13 алгоритма.

2)Снять временные диаграммы работы JK=триггера 7472, выполнив пункт 14 алгоритма.

3)Составить таблицу истинности JK-триггера 7472, выполнив пункт 15 алгоритма.

Провести схемотехническое моделирование JKтриггера 7472 (отечественный аналог К155ТВ1)

Вданном триггере имеется один универсальный JKтриггер с тройными J и K входами И. Они принимают данные, когда S=R=B. Триггер двухступенчатый. Для тактового входа требуется полный импульс . Положительным фронтом комбинация JK загружается в триггер-мастер . Она переносится в триггер-помощник отрицательным срезом и появляется на выходах Q и Q. Во время вершины тактового импульса С=В сигналы JK менять нельзя. .

Схема измерения приведена на рис.6.6, в табл. 6.2 приведена форма таблицы истинности.

Таблица 6.2 Форма таблицы истинности триггера 7472

|

|

|

|

|

|

_ |

S |

R |

C |

J |

K |

Q |

Q |

На рис. 6.7 представлен функциональный состав триггера 7472 , форма таблицы истинности для него приведена в табл. 6.2.

92 |

93 |

Рис. 6.6. Схема измерения триггера 7472

Рис. 6.7. Функциональная схема триггера 7472

Провести схемотехническое моделирование JKтриггера 74107 (отечественный аналог К155ТВ6)

Микросхема не содержит вход установки S . Ноль и единица, подготовленные на входах J и K, загружаются в триггер во время положительного перепада импульса С. Срез перепада импульса С от высокого к низкому переносит их на выходы. Для данной микросхемы сбросу Q=Н наступает при R=Н ( остальные входы в этот момент безразличны).

Схема измерения представлена на рис. 6.8 , в табл. 6.3 приведена форма таблицы истинности данного триггера .

Рис. 6.8. Схема измерения триггера 74107

Таблица 6.3 Форма таблицы истинности триггера 74107

|

|

|

|

|

_ |

R |

C |

J |

K |

Q |

Q |

|

|

|

|

|

|

Провести схемотехническое моделирование JKтриггера 74109 (отечественный аналог К155ТВ15)

Особенности этого триггера в том, что вход J- прямой, а К - инверсный , запись происходит положительным перепадом импульса С.

94 |

95 |

Схема измерения представлена на рис. 6.9, форма таблицы истинности триггера 74109 находится в табл. 6.4 .

Рис. 6.9. Схема измерения триггера 74109

Таблица 6.4 Форма таблица истинности триггера 74109

_

R |

S |

C |

J |

K |

Q |

Q |

Функциональный состав триггера 74109 представлен на рис. 6.10.

Рис. 6.10. Функциональный состав триггера 74109

Провести схемотехническое моделирование JKтриггера 74110

Эта микросхема имеет по три входа J и K, вход синхронизации, а так же входы сброса и установки. Эта микросхема характерна тем, что при подаче на ее входы J и K одинаковых сигналов увеличивается ее быстродействие.

Схема измерения триггера 74110 приведена на рис. – 6.11 , в табл. 6.5 приведена форма таблицы истинности JKтриггера 74110.

96 |

97 |

Рис. 6.11. Схема измерения триггера 74110

|

|

|

|

|

|

|

|

Таблица 6.5 |

||

|

|

Форма таблица истинности триггера 74110 |

||||||||

|

|

|

|

|

|

|

|

|

_ |

|

S |

|

R |

C |

J |

|

K |

Q |

|

Q |

|

|

Провести |

схемотехническое |

моделирование jk- |

|||||||

триггера 74111

Схема измерения триггера 74111 изображена на рис. 6.12. Для данной микросхемы временные диаграммы и таблица истинности аналогичны результатам, полученным при анализе триггера 74110.

98

Рис. 6.12. Схема измерения триггера 74111.

Параметры генераторов

Для проведения работы необходимо: найти в библиотеке элементов нужную микросхему. Если требуется, то раскрывается внутренняя структура триггера. Далее в библиотеке элементов нужно отыскать генераторы напряжений, необходимые логические элементы, расставить и соединить их с помощью «карандаша» на основании табл.6.6.

Таблица 6.6 Параметры генераторов цифровых сигналов

Микро-схема |

|

|

|

|

П А Р А М Е Т Р Ы |

|

|

|||

№ Вар. |

Вход |

Источник |

DELAY µS |

ONTIME µS |

OFFTIME µS |

|

STARTVAL |

OPPVAL |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

DSTM1 |

0 |

|

1 |

1 |

|

0 |

1 |

|

|

K |

DSTM2 |

0.5 |

|

1.5 |

1.5 |

|

0 |

1 |

7440 |

|

C |

DSTM3 |

3 |

|

0.5 |

0.5 |

|

0 |

1 |

1 |

R |

DSTM4 |

1.5 |

|

2 |

2 |

|

0 |

1 |

|

S |

DSTM5 |

1 |

|

1.5 |

1.5 |

|

0 |

1 |

||

|

|

|

|

|||||||

|

|

J |

DSTM1 |

0 |

|

2 |

2 |

|

0 |

1 |

|

|

K |

DSTM2 |

1 |

|

3 |

3 |

|

0 |

1 |

|

|

|

|

|

99 |

|

|

|

|

|