книги / Реализация цифровых автоматов в системе Quartus фирмы Altera

..pdf

Рис. 15. Создание VHDL-файла проекта

В результате будет создан файл с описанием автомата на языке VHDL. После этого нужно откомпилировать проект Proc- essing->Start Compilation. В случае успешной компиляции необходимо промоделировать синтезированное микропрограммное устройство управления. Временные диаграммы должны иметь вид, показанный на рис. 16.

Рис. 16. Результаты моделирования автомата

111

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Угрюмов Е.П. Цифровая схемотехника: учебное пособие для вузов. – 2-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2007. – 800 с.

2.Тюрин С.Ф. Вычислительная техника и информационные технологии. Цифровая схемотехника: учеб. пособие. – Пермь: Изд-во Перм. гос. техн. ун-та, 2008. – 137 с.

3.Аляев Ю.А., Тюрин С.Ф. Дискретная математика и математическая логика. – М.: Финансы и статистика, 2006. – 357 с.

4.Тюрин С.Ф. Дискретные устройства (автоматы) систем автоматизированного управления и контроля: руководство для лабораторных работ / ПВВКИКУ. – Пермь, 1994. – 93 с.

5.Тюрин С.Ф. Дискретные устройства (автоматы) систем автоматизированного управления и контроля: конспект лекций / ПВВКИКУ. – Пермь, 1996. – 361 с.

6.Тюрин С.Ф., Аляев Ю.А. Дискретная математика: практическая дискретная математика и математическая логика. – М.: Финансы и статистика, 2010. – 394 с.

112

ПРИЛОЖЕНИЕ 1

Дополнительные сведения по системе Quartus II. Виды конструкторских файлов пакета Quartus II

Конструкторский файл устройства – это главный файл проекта, он содержит функционально-логическое описание устройства. Пакет Quartus II поддерживает ввод описания проекта из нескольких типов конструкторских файлов, в том числе:

– AHDL File – файл на языке описания аппаратуры фирмы

Altera (AHDL – Altera Hardware Description Language);

–Block Diagram/Schematic File – файл в виде графического представления схемы или блок-схемы проекта;

–EDIF File – файл в формате обмена электронными проек-

тами (Electronic Design Interchange Format);

–State Machine File – файл конечно-автоматного представления;

–Verilog HDL File – файл на универсальном языке описания аппаратуры Verilog;

–Tcl script File – Tcl (от англ. Tool Command Language —

«командный язык инструментов», читается «тикль») — скриптовый язык высокого уровня. Tcl часто применяется совместно с графической библиотекой Tk (Too Kit). Связку Tcl/Tk по-русски иногда называют «Так-тикль».

–VHDL File – файл на универсальном языке описания ап-

паратуры VHDL (Very High Speed Integrated Circuit Hardware

Description Language).

Эти типы файлов представлены в списке для выбора на за-

кладке «Design Files» окна «New».

Окно временного моделирования

Окно состоит из двух частей: левой – «Report Window Contents» («Содержание окна отчета»), в которой можно выбрать требуемый раздел отчета о моделировании, и правой – «Report Window Section» («Демонстрационная секция отчета»), в кото-

113

рой представлено содержание выбранного раздела отчета. По умолчанию в демонстрационной секции представлен раздел

«Simulator\Simulation Waveforms» («Симулятор\Диаграммы мо-

делирования»). Если раздел оказался неподключенным, например, если вы запускали симулятор из окна «Simulator Tool», его следует подключить, выбрав соответствующую строку в списке

«Report Window Contents».

Особенности ПЛИС Cyclone III

Семейство Cyclone III относится к архитектуре FPGA. Микросхемы изготавливаются по 65 нм технологии, выпущены на рынок весной 2007 г. Стоимость микросхемы EP3C5E144C8 около 17 $. Она выпускается в корпусе EQFP (Plastic Enhanced Quad Flat Pack), что дает возможность устанавливать ее на печатной плате без специального оборудования (с помощью обычной паяльной станции).

В микросхемах FPGA фирмы Altera конфигурация проекта (схема устройства) хранится в специальных внутренних ячейках памяти типа SRAM (Static Random Access Memory). Эта память теряет информацию после выключения питания. Поэтому кроме микросхемы ПЛИС на печатной плате устройства должна быть установлена энергонезависимая память, из которой каждый раз при подаче питания конфигурационные данные автоматически загружаются в FPGA.

Другим вариантом является подключение микросхемы FPGA специальным кабелем к компьютеру или микроконтроллеру, осуществляющим загрузку. Микросхемы поддерживают внутрисхемное программирование (ISP) с помощью устройства «Byte-Blaster MV», подключаемого к принтерному порту компьютера и управляемого непосредственно из пакета Quartus II.

114

ПРИЛОЖЕНИЕ 2

Реализация логической функции z мультиплексирования восьми переменных а, b, с, d, e, f, g, h (генератора функций трех аргументов)

в функционально-полном толерантном базисе

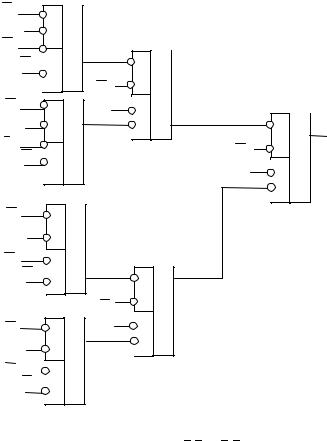

Необходимы три каскада ФПТ [5,8] элементов. Соответствующая схема представлена на рис. П2.1. Представим логическую схему мультиплексора в САПР Quartus II, причем ФПТ-элемент моделируем изпростыхисложныхэлементов библиотеки.

c |

& 1 |

x1 |

|

d |

& |

x1 |

|

a |

& 1 |

x1 |

|

b |

& |

x1 |

|

g |

& 1 |

|

|

x1 |

|

h |

& |

|

|

x1 |

|

e |

& 1 |

|

|

x1 |

|

f |

& |

x1 |

|

x2

x2

x2

x2

& |

1 |

& |

|

& |

1 |

& |

|

|

& |

1 |

z |

|

|

|

|

х3 |

|

|

|

х3 |

& |

|

|

Рис. П2.1. Генератор функций трех аргументов в ФПТ базисе x1 x2 x3 x4

115

а |

б |

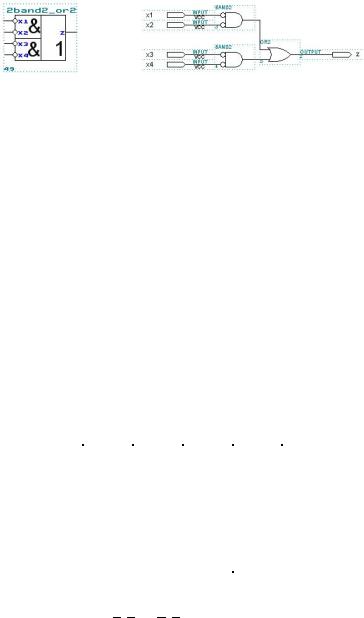

Рис. П2.2. Модель ФПТ элемента как сложный элемент «2И-НЕ-2ИЛИ»: а – символ ФПТ элемента; б – логическая схема модели элемента

Сложный элемент «2И–НЕ–2ИЛИ» (рис. П2.2) является базисным и изображен как символ (рис. П2.2, а). Он составлен из простых элементов (рис. П2.2, б) и занесен в библиотеку функ- ционально-полных толерантных схем как базисный элемент, из которого строятся все последующие схемы.

Для завершения работы над проектом необходимо провести функциональное моделирование. САПР Quartus II позволяет проверить правильность реализованной схемы путем симуляции непосредственно перед конфигурированием ПЛИС.

Проверка реализованной схемы осуществляется сравнением таблицы истинности с временными диаграммами. Убедившись, что временная диаграмма полностью соответствует таблице истинности мультиплексора (табл. П2.1), рассмотрим поведение работы мультиплексора с заданной моделью отказов.

Таблица П2 . 1

x1 |

x2 |

x3 |

z |

0 |

0 |

0 |

a |

0 |

0 |

1 |

b |

0 |

1 |

0 |

c |

0 |

1 |

1 |

d |

1 |

0 |

0 |

e |

1 |

0 |

1 |

f |

1 |

1 |

0 |

g |

1 |

1 |

1 |

h |

Схема генератора функций реализована на семи ФПТэлементах с базисом x1 x2 x3 x4 .

116

Графический (схемный) способ ввода функционально-логического описания проекта

впакете Quartus II

1.Запустить приложение Quartus II, выбрать в строке меню

«File\New Project Wizard...» («Файл\МастерСозданияпроекта...»).

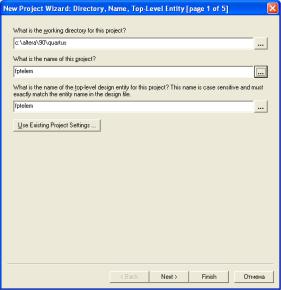

2.В появившемся окне «New Project Wizard: Directory, Name, and Top-Level Entity [page 1 of 5]» щелкнуть по кнопке

стремя точками у верхнего поля ввода (рис. П2.3) и в новом окне «Select Directory», переместившись в желаемое место на диске, создать новую папку для начинаемого проекта устройства и «зайти» в нее. После этого щелкнуть по кнопке «Открыть»

окна «Select Directory».

Рис. П2.3. Окно задания папки, имени проекта

иимени модуля верхнего уровня

3.После возвращения в окно «New Project Wizard: Directory, Name, and Top-Level Entity [page 1 of 5]» убедиться в том, что

вверхнем поле ввода занесен полный маршрут ко вновь создан-

117

ной папке, во втором поле – имя проекта, совпадающее с именем папки, и в третьем (нижнем) поле – имя модуля верхнего уровня, также совпадающее с именем папки.

4.Выбрать в строке меню «File\New...». В появившемся окне

«New» на закладке «Design Files» выбрать строку «Block Diagram/Schematic File» («Файл блок-схемы/Схемный файл»). Щелкнуть по кнопке «ОК» в нижней части окна. На рабочем поле приложения появится окно созданного файла с именем Blockl.bdf. Его расширение означает, что это «Block Design File», т.е. файл с графическим представлением проектаввидесхемы.

5.Выбрать в строке меню «File\Save As...». В появившемся диалоговом окне «Сохранить как» будет предложено сохранить файл с именем проекта и расширением bdf. Далее необходимо решить основную задачу проектирования – ввести описание логики устройства в виде схемы, состоящей, в нашем случае, из элементарных логических элементов (см. рис. П4.2, б).

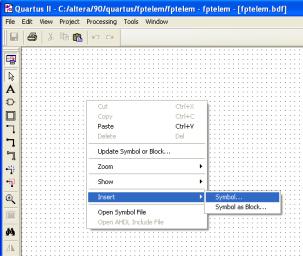

6.Щелкнуть правой кнопкой мыши по рабочему полю файла *.bdf. В появившемся контекстном меню выбрать строку «Insert» и далее «Symbol...», как это показано на рис. П2.4.

Рис. П2.4. Контекстное меню для произвольной точки на рабочем поле схемного конструкторского файла (*.bdf)

118

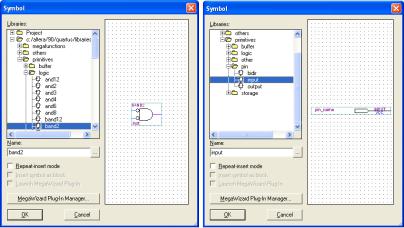

7. После выполнения команды контекстного меню «Insert\Symbol...» на экране появится окно «Symbol» (рис. П4.5, а).

В поле «Libraries:» выбрать элемент band2. Поместить его в удобное место и щелкнуть левой кнопкой мыши. Элемент будет установлен на рабочем поле (рис. П2.5).

а |

б |

Рис. П2.5. Окно ввода символов

Сделать копию элемента band2.

8.Таким же образом, как и элементы band2, вывести на рабочееполеконструкторскогофайлаэлемент оr2 (см. рис. П2.2, б).

9.Повторить действия, необходимые для вывода символа логического элемента, но на стадии выбора раздела библиотеки «primitives» вместо раздела «logic» открыть расположенный ниже в том же списке раздел «pin» («вывод»). Выделить символ вывода input (вход) и щелкнуть по кнопке «ОК». Установить появившийся на рабочем поле символ входного вывода в левом верхнем углу.

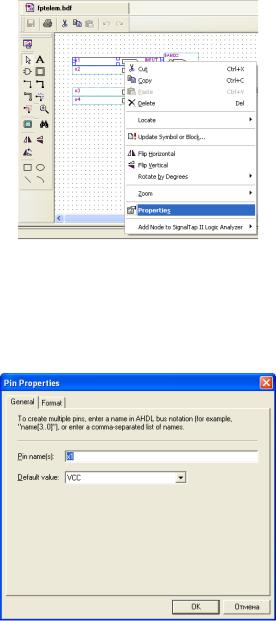

10.Щелкнуть правой кнопкой по символу входного вывода на рабочем поле. В появившемся контекстном меню выбрать строку «Properties...» (рис. П2.6).

119

Рис. П2.6. Выделенный вывод и его контекстное меню

11. В появившемся окне «Pin Properties» в верхнем поле ввода «Pin Name(s):» ввести с клавиатуры имя первого входного вывода – x1. В расположенном ниже списке ввода «Default value:», нажав на кнопку вызова списка, выбрать в нем значение «VCC». Щелкнуть по кнопке «ОК» (рис. П2.7).

Рис. П2.7. Окно «Pin Properties» («Свойства Вывода»)

120