- •Автоматизация измерений, контроля и испытаний

- •Введение. Основные определения и термины

- •1. Принципы построения измерительных систем

- •1.1. Ввод аналоговых сигналов в измерительных системах

- •1.1.1. Датчики измерительных систем и устройства согласования

- •1.1.2. Измерительные коммутаторы

- •1.1.3. Аналого-цифровые и цифро-аналоговые преобразователи

- •1.2. Оценка системных параметров многоканальных измерительных систем

- •1.3. Каналы передачи данных (интерфейс)

- •1.4. Устройства и системы ввода/вывода фирмы National Instruments

- •1.4.1. Системы согласования сигналов scxi и scc

- •1.4.2. Многофункциональные платы и устройства для сбора данных

- •1.4.3. Модульные измерительные системы стандарта pxi

- •1.4.4. Система распределенного ввода/вывода и промышленного управления FieldPoint

- •1.4.5. Реконфигурируемая контрольно-измерительная система CompactRio

- •1.5. Система дистанционного измерения и сбора измерительно-диагностической информации

- •1.5.1. Общая структура системы

- •1.5.2. Измерительная часть автоматизированной системы дистанционных измерений

- •1.5.3. Алгоритмы работы автоматизированной системы дистанционных измерений

- •1.5.4. Разработка схем подключения средств измерения

- •2. Сигналы и методы их исследования

- •2.1. Общие характеристики электрических сигналов

- •2.2. Методы исследования прохождения сигналов

- •2.3. Динамические модели преобразователей сигналов

- •2.4. Механические, тепловые и электрические аналогии

- •2.4.1. Механические элементы

- •2.4.2. Тепловые элементы

- •2.4.3. Электрические элементы

- •2.5. Фильтры

- •2.5.1. Фильтры нижних частот

- •2.5.2. Фильтры верхних частот

- •2.5.3. Полосовые фильтры

- •2.5.4. Полосно-подавляющие фильтры

- •3. Аналоговая обработка сигналов

- •3.1. Операционные усилители. Основные свойства

- •3.2. Параметры и характеристики оу

- •3.3. Обратная связь в усилителях

- •3.4. Влияние ос на параметры усилителей

- •3.5. Применение операционных усилителей

- •3.5.1. Инвертирующий усилитель

- •3.5.2. Неинвертирующий усилитель

- •3.5.3. Суммирующий усилитель

- •3.5.4. Дифференциальный усилитель

- •3.5.5. Измерительный усилитель

- •3.5.6. Интеграторы

- •3.5.7. Дифференциаторы

- •3.5.8. Нелинейные преобразователи на оу

- •3.6. Активные фильтры

- •4. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.1. Электронные ключи и коммутаторы

- •4.2. Цифро-аналоговые преобразователи

- •4.2.1. Общие положения

- •4.2.2. Цап с суммированием токов

- •4.2.3. Цап с внутренними источниками тока

- •4.2.4. Сегментированные цап

- •4.4.5. Цифровые потенциометры

- •4.2.6. Цап прямого цифрового синтеза

- •4.2.7. Параметры цап

- •4.3. Аналого-цифровые преобразователи

- •4.3.1. Общие положения

- •4.3.3. Ацп последовательного приближения

- •4.3.4. Последовательно-параллельные ацп конвейерного типа

- •4.3.5. Сигма-дельта ацп

- •5. Цифровая обработка сигналов

- •5.1. Общая характеристика цифровых сигналов и цифровых микросхем

- •5.2. Основы алгебры логики

- •5.3. Логические элементы

- •5.3.1. Типы логических элементов

- •5.3.2. Параметры логических элементов

- •5.4. Построение комбинационной логической схемы по заданной функции. Минимизация логических функций

- •5.5. Типы выходных каскадов цифровых элементов

- •5.6. Сложные логические элементы

- •6. Функциональные устройства на цифровых микросхемах

- •6.1. Системы счисления

- •6.2. Дешифраторы и шифраторы

- •6.3. Мультиплексоры и демультиплексоры

- •6.4. Компараторы кодов

- •6.5. Сумматоры

- •6.6. Триггеры

- •6.7. Регистры

- •6.8. Счетчики импульсов

- •6.9. Автоматизированные измерительные системы

- •Заключение

- •Библиографический список

- •394026 Воронеж, Московский просп., 14

5.3.2. Параметры логических элементов

Из рассмотрения схем различных логических элементов следует, что они представляют собой многоэлементные устройства, поэтому работоспособность логических элементов характеризуется набором основных параметров и только их совокупность позволяет сравнивать между собой и классифицировать различные электронные логические схемы.

Рис. 5.12. Передаточная характеристика

инвертирующего ЛЭ

Четыре значения напряжений задают границы отображения переменных («0» и «1») на выходе и входе элемента. Для нормальной работы элемента требуется, чтобы напряжение, отображающее логическую «1», было достаточно высоким, а напряжение, отображающее логический «0», — достаточно низким. Эти требования задаются параметрами U1вх.мин и U0вх.макс (точки D и B на рис. 5.12). Касательные к характеристике в этих точках имеют наклон –45, т. е. это точки единичного усиления. Уровни, гарантируемые на выходе элемента при соблюдении допустимых нагрузочных условий, задаются параметрами U1вых.мин и U0вых.макс. Между этими токами заключена активная область, в которой усиление схемы больше единицы. Внутри активной области находится точка C, называемая пороговой точкой. Прямая, соединяющая начало координат с точкой, имеет наклон к координатным осям 45. Очевидно, что при сигнале на входе меньшем Uпор сигнал на выходе будет стремиться к U1, а большем Uпор — к U0. Это формирующее свойство является основополагающим для ЛЭ и определяет помехоустойчивость ЛЭ по отношению к сигналам помехи. Входные напряжения данного элемента есть выходные напряжения предыдущего (источника сигналов). Разность этих уровней дает размах логического сигнала ΔUл. Точка A определяется на характеристике как точка, абсцисса которой равна U0вых.макс. Точка E имеет абсциссу U1вых.мин. Прямая, соединяющая точки A и E, имеет наклон к координатным осям –45. Для уровня U1 опасны отрицательные помехи, снижающие его. Напряжение U0п есть напряжение допустимой статической помехи (т. е. помехи любой длительности), которое, будучи приложено к входу схемы при действии на нем логического нуля, еще не сможет переключить схему. Аналогично определяется U1п для схемы, на входах которой действуют напряжения логической единицы. Отсюда помехоустойчивость U0п=U0вх.макс–U0вых.макс, U1п=U1вых.мин–U1вх.мин. Иногда восприимчивость схемы к помехам (помехозащищенность) измеряют как разности напряжений рабочих точек и пороговой точки. Таким образом, пороговая точка С ограничивает предельные значения входного сигнала ЛЭ, т. е. U0вх.макс и U1вх.мин.

При сравнении ЛЭ с различными уровнями «0» и «1» часто используют безразмерные параметры P1п=U1п/U1п–U0п и P0п=U0п/U1п––U0п, называемые коэффициентами помехоустойчивости ЛЭ.

Динамическая помехоустойчивость (помехоустойчивость в динамическом режиме) зависит от длительности, амплитуды и формы сигнала помехи, а также от уровня статической помехоустойчивости и скорости переключения логического элемента.

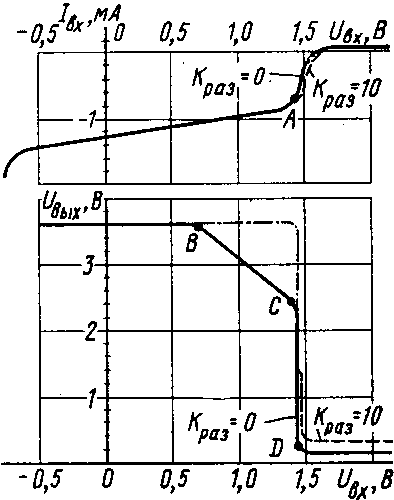

Четыре значения токов — входные и выходные токи в обоих логических состояниях оценивают по входной и выходной характеристикам, рис. 5.13 и 5.14. При высоком уровне выходного напряжения из элемента-источника ток вытекает, цепь нагрузки ток поглощает. При низком уровне выходного напряжения элемента-источника ток нагрузки втекает в этот элемент, а из входных цепей элементов-приемников токи вытекают. Зная токи I1вых.макс и I0вых.макс, характеризующие возможности элемента-источника сигнала, и токи I1вх.макс и I0вх.макс, потребляемые элементами-приемниками, можно контролировать соблюдение нагрузочных ограничений, обязательное для всех элементов схемы цифрового устройства.

Рис. 5.13. Входная и передаточная

характеристики элемента ТТЛ

Рис. 5.14. Входная характеристика элемента

ТТЛ

коэффициент разветвления по выходу n — характеризует количество других элементов данной серии, которые могут быть подключены к выходу данного элемента без нарушения его работоспособности. Нагрузочная способность выпускаемых логических схем в значительной степени определяется характеристиками инвертора. Для обычных инверторов n=4—10, а для мощных инверторов и схем на МОП-транзисторах n= =30—50. Нагрузочная способность элемента определяется его выходным сопротивлением;

коэффициент объединения по входу m — характеризуется количеством входов данного логического элемента (от двух и более). Так как входными схемами являются схемы И или ИЛИ, то коэффициент объединения по входу зависит от возможностей этих схем. Для схем И m=3—8, для схем ИЛИ m=3—4. Для увеличения числа т в серии ИС обычно предусматривают «расширители по И» и «расширители по ИЛИ».

Рис. 5.15. Временные диаграммы

процессов переключения логического

элемента

На рис. 5.15 представлены совмещенные диаграммы изменения входного и выходного напряжений инвертирующего логического элемента и указаны динамические параметры. Среднее время задержки выходного сигнала tз.ср определяется как среднее времен включения tз1,0 и выключения tз0,1. Отметим, что tз.ср определяется не только свойствами самого ЛЭ, но зависит от емкости на входе и емкости нагрузки. Следовательно, tз.ср зависит от коэффициентов объединения по входу и разветвления по выходу. Времена нарастания tф0,1 и спада tф1,0 мало зависят от характера входного сигнала.

Для схем малого быстродействия среднее время задержки 400 нс, для схем среднего быстродействия 20—50 нс, для высокого быстродействия менее 10 нс.

На быстродействие цифрового устройства влияют также емкости, на перезаряд которых требуются затраты времени. В справочных данных приводятся входные и выходные емкости логических элементов, знание которых позволяет подсчитать емкости нагрузки в узлах схемы. Для подключаемой к выходу элемента емкости приводятся две цифры: номинальная емкость Cн и предельно допустимая емкость Смакс. Первая емкость соответствует условиям измерения задержек сигналов, так что именно для нее справедливы значения задержек сигналов, приведенные в справочных данных. Если реальная нагрузочная емкость отличается от номинальной, то изменятся и значения задержек. Значения реальных задержек можно оценить с помощью соотношения tз=tз.н+kС, где tз.н — номинальное значение задержки; С=С–Cн; C — фактическое значение нагрузочной емкости; k — коэффициент, величина которого задается для каждой серии элементов индивидуально. Предельно допустимая емкость указывает границу, которую нельзя нарушать, поскольку при этом работоспособность элемента не гарантируется. Разумеется, при подсчете емкостей в узлах цифрового устройства учитываются и емкости межсоединений (монтажные емкости).

Потребляемая мощность Pср логических схем зависит от характера входных сигналов. Поэтому различают P0 — мощность, потребляемую схемой в статическом состоянии 0; P1 — мощность, потребляемую в статическом состоянии 1; P01, P10 — мощности при переходе из 0 в 1 и обратно. Потребляемую мощность принято определять в статическом режиме (пренебрегая процессами перехода) и считать, что длительность состояния 0 равна длительности состояния 1. В этом случае

Pср=(P0+P1)/2.

Экономичность и быстродействие логических ИС часто оценивают с помощью комплексного параметра — произведения средней потребляемой мощности на среднее время задержки. Желательно, чтобы это произведение имело минимальную величину.